첨단 패키징에 대해 공부한 글을 공유합니다. 염승환 이사님의 함께 배우기를 참고하며 요약한 글입니다. 이해한 내용을 c최대한 쉽게 작성하고자 하였습니다. 문과생 직장인으로, 초보 입문자를 위한 글이니 혹여 틀리거나 지적할 부분이 있다면 언제든지 환영합니다.

첨단패키징

전통적인 패키징보다 첨단 패키징이 성장율이 높아집니다. 기존의 한개 칩만 패키징하는 방식보단 이종 칩 간의 결합, 수직 적층 등 고사양의 칩을 만들기 위해 첨단 방식의 수요가 높아지는 추세입니다.

패키징은 칩과 기판을 연결하는 공정입니다. 칩이 반도체 역할을 하기 위한 최종적인 과정이죠. 보호하는 기능도 수행합니다. 기존에는 전공정 단의 미세화가 고사양을 위한 기술 개발의 핵심이었습니다. 하지만 미세화를 위한 비용 투자가 금액대비 성능 향상 폭이 미미하기에 후공정 부각되기 시작하게 된거죠. 한마디로 전공정은 투입대비 가성비가 떨어지니 후공정에 관심을 갖게 된 거고, AI가 그 수요를 촉발 시킨겁니다.

연결(본딩)

구리선으로 연결하는 와이어 본딩이 전통적 방식이고 현재는 플립칩이 주로 쓰이게 됩니다. 선으로 연결하던 방식을 범프라는 작은 Ball을 사용하여 연결하는 방식이죠. FC-BGA는 첨단 패키징의 방식 중 하나입니다

선보다는 기판과 다이가 접촉면이 많아지기에 칩의 성능은 더 좋아지게 됩니다.

WLP(Wafer level Package)

전통 방식은 웨이퍼를 자르고 개별 패키징을 진행하였습니다. 반면, WLP는 가공 완료된 웨이퍼 위에서 직접 패키징을 먼저합니다. RDL 재배선 층을 먼저 설치하고 그리고 절단을 합니다. TSMC가 해당 패키징 기술로 부각받기 시작하였습니다.

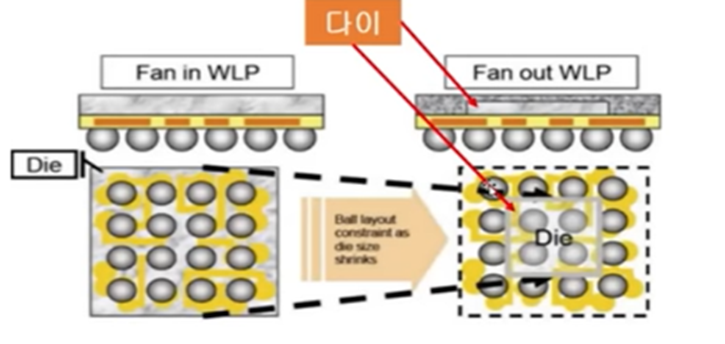

WLP에도 종류가 있습니다. FO와 FI 방식으로 나뉩니다.아래 그림을 보며 이해하면 쉽습니다.

칩과 기판의 크기가 거의 같은 방식을 FI방식, 칩보다 기판이 더 큰 경우를 FO방식이라고 합니다.

FI(Fan In)은 다이와 기판의 크기가 비슷해 I/O(입출력단자)를 늘리는데 한계가 있습니다. 반면 FO(Fan Out)은 다이보다 기판이 크기 때문에 I/O를 칩 밖으로 빼낸 방식으로 I/O(입출력단자) 면적 확대하여 칩 성능을 극대화 할 수 있는 장점이 있습니다. 입출력 단자는 쉽게 보면 데이터이동 통로로, 도로라고 생각하면 쉬울 것 같네요. 도로가 많을 수록 속도는 더 빠르다고 생각하시면 쉬울 것 같네요.

해당 기술로 TSMC가 삼성대비 경쟁 우위를 갖게됩니다. 물론, 애플 입장에서 삼성은 핸드폰을 제조하는 경쟁사라는 이유도 있었겠지만요

CoWos(Chip on Wafer On Substrate)

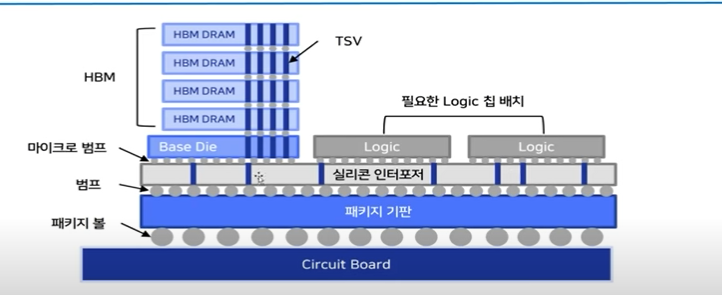

서로 다른 칩을 인토포저를 통해서 하나로 연결하는 패키징입니다. 2.5d 패키징이라고도 부르죠. 이 분야의 전문가 역시 TSMC입니다.

인터포저는 집적 회로의 배선 연결을 도와주는 부품입니다. 인터포저는 사이에 넣다는 의미하는 라틴어인 Interponere에서 유래했다고 하네요. 실리콘을 사용하면 열적 안정성을 보유하는 장점이 있습니다. 삼성전자는 I-CUBE란 브랜드로 해당 패키징을 구현하고 있습니다.

CoWos는 디램(메모리)과 CPU/GPU(비메모리)의 서로 다른 이종칩을 한 기판에 패키징하여 성능을 높이는 방식입니다.

쉽게 생각하죠. 기존에는 멀리 떨어져 있다가 가까워지는 송수신이 더 빨라지겠죠?

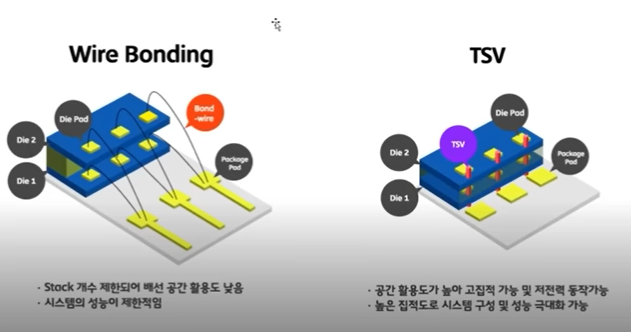

와이어본딩 VS TSV

와이어본딩은 선으로 연결하는 전통적인 패키징 방식. TSV는 구멍을 뚫어 위아래 연결하는 첨단 패키징입니다.

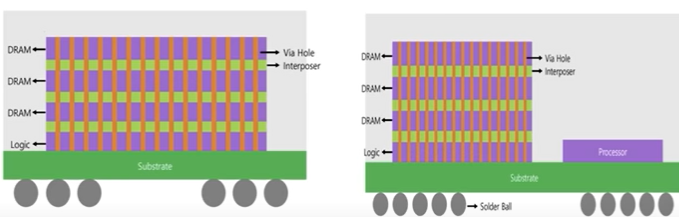

TSV(Through Silicon Via, 작은통로)는 칩의 실리콘 기판을 통과하는 수직 전기 연결을 생성하는 기술입니다.

와이어나 플립칩에 비해 더 짧은 인터커넥트 길이로 빠른 전기 신호 전달이 가능하고 고대역폭이며 전력 소모가 감소하는 강점을 지녔습니다. 즉 선보다 직접 붙어있기에 더 빠른 성능을 구현하게 됩니다. 그리고 수 많은 디램을 위로 쌓았기에 공간의 효율성도 있습니다.

TSV를 하기 위해서는 전공정도 필요합니다.

과정을 보면 구멍을 뚫기 위해 식각을 한 뒤, 구리 금속을 넣습니다. 증착을하는 거죠. 다음에는 CMP 평탄화 작업을 거칩니다. 그런 뒤 후공정을 진행하게 됩니다. 아래 그림을 첨부했는데 디테일 할 수록 어렵네요

건식 식각은 램리서치, AMAT. 구리 증착은 테스. CMP는 케이씨텍. 세정은 제우스입니다

(관련 기업이긴 하나 실제로 연관된지는 확인이 필요해보입니다)

위의 패키징 설명한 방식을 토대로 AI반도체 밸류체인을 정리해보며 글을 마칩니다.

최초 엔비디아는 자사의 인공지능 반도체를 제조하기 위해 하이닉스에 HBM을 의뢰합니다. HBM을 의뢰받은 하이닉스는 TSV공법으로 HBM을 제조합니다. 그 뒤, 해당 칩은 TSMC로 넘어가서 2.5D 패키징을 통해 인공지능 반도체가 만들어지게 되죠. 세부적인 내용은 더 많습니다만 큰 틀에서 이해해보고 디테일을 찾아보고 해당 기업을 공부하는게 도움이 되리라 생각합니다. 저 역시 그런 과정에서 이렇게 그을 남기고 있습니다.

다음편에서 더 내용을 다뤄보겠습니다.

감사합니다.

'산업공부' 카테고리의 다른 글

| 24년 주식전망_섹터별(펌글) (0) | 2024.01.15 |

|---|---|

| 첨단 패키징 배우기2_HBM/TC본딩/MR-MUF/레이저리플로우 (0) | 2024.01.15 |

| 반도체 현황 밸류체인_240112 (0) | 2024.01.12 |

| HBM4 반도체와 관련기업 (1) | 2024.01.09 |

| 웹툰산업 밸류체인 Feat_네이버웹툰 상장 (0) | 2024.01.03 |